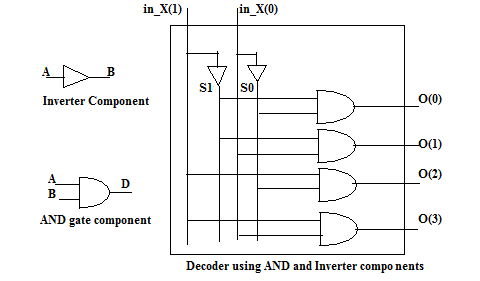

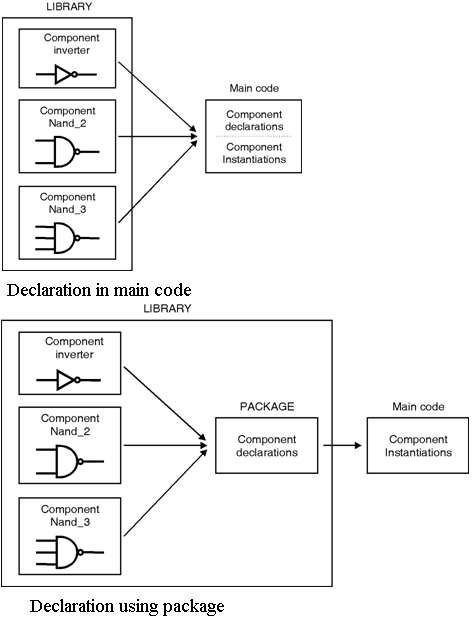

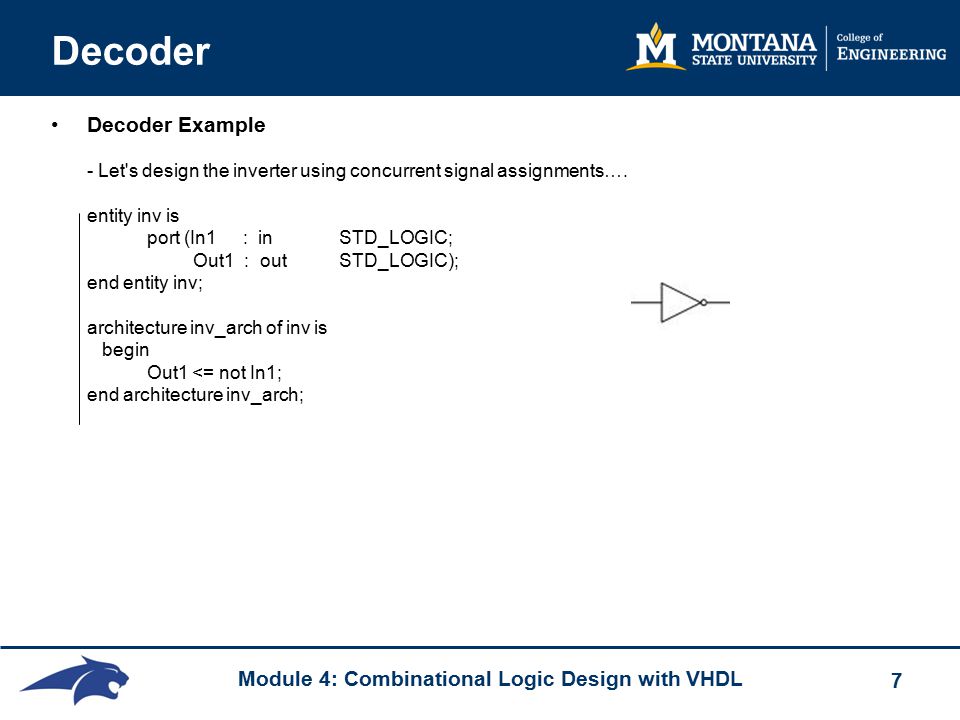

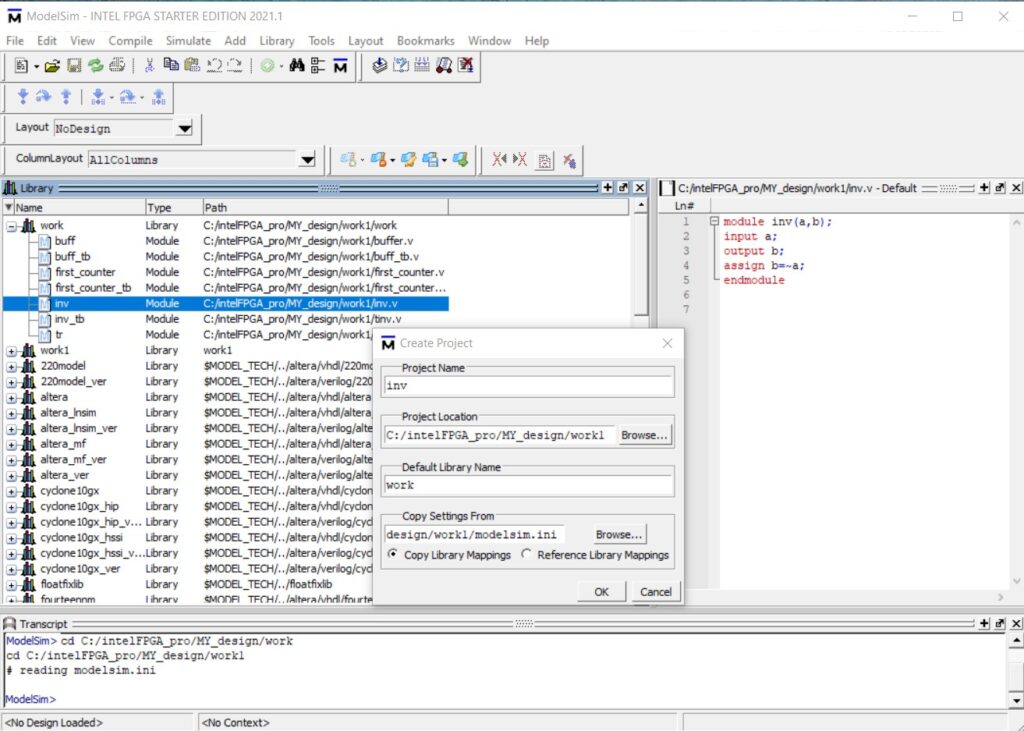

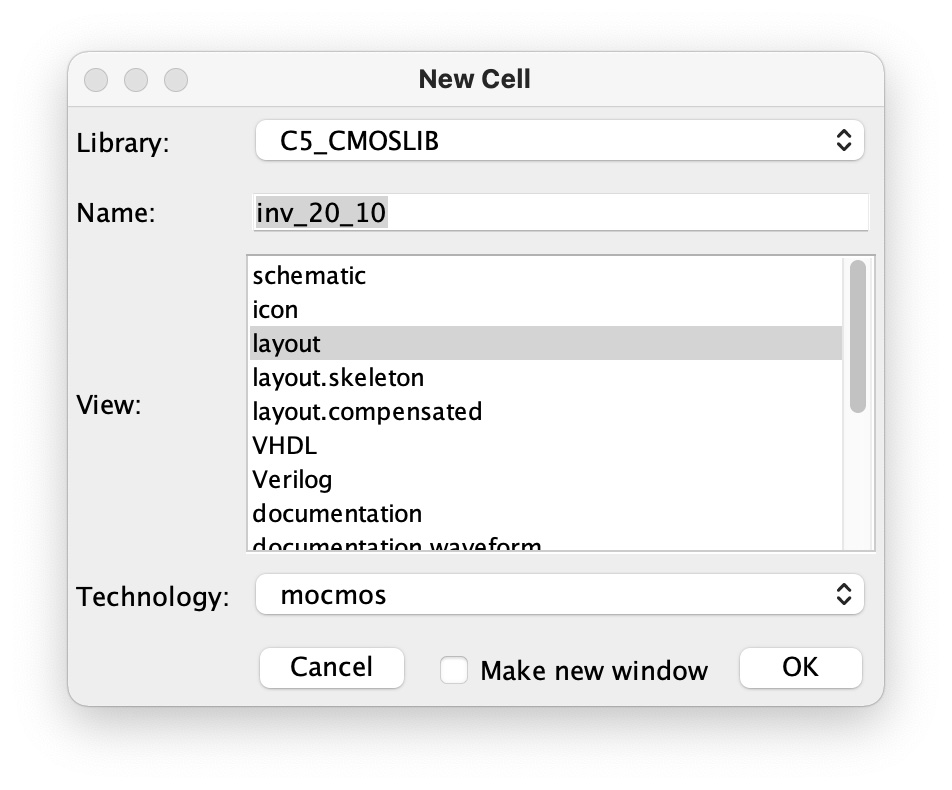

A short description of VHDL code of the framework, (a) inverter circuit... | Download Scientific Diagram

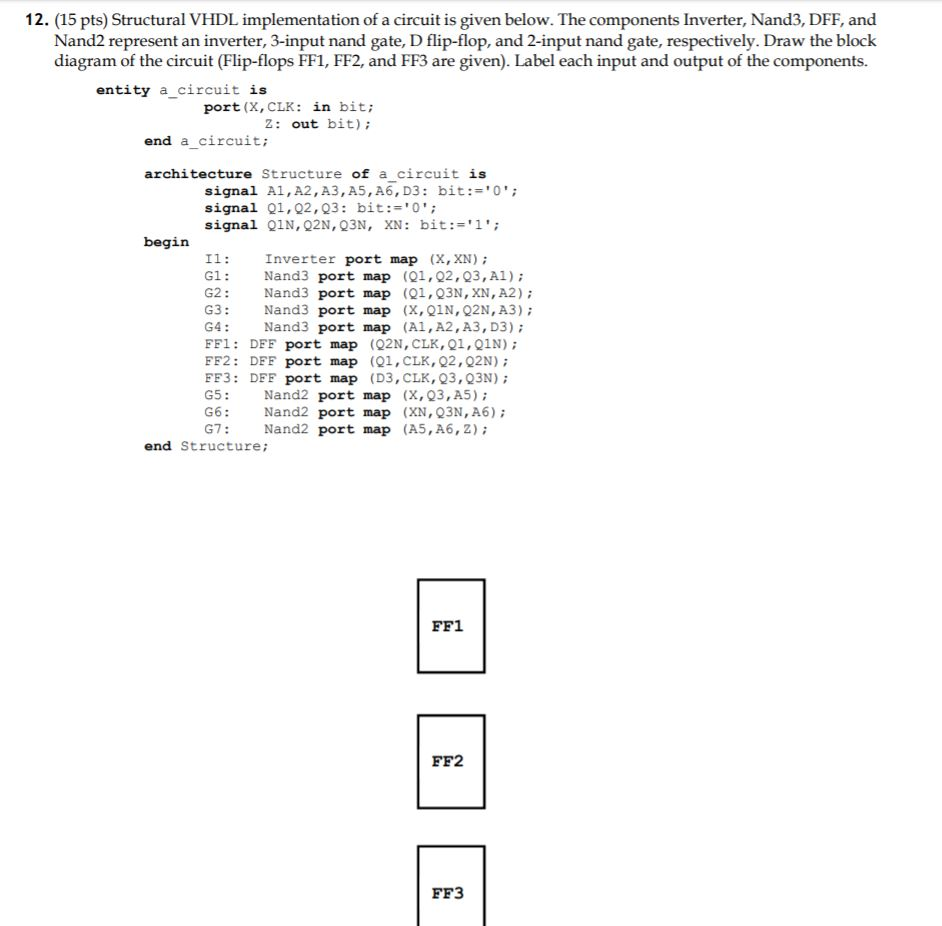

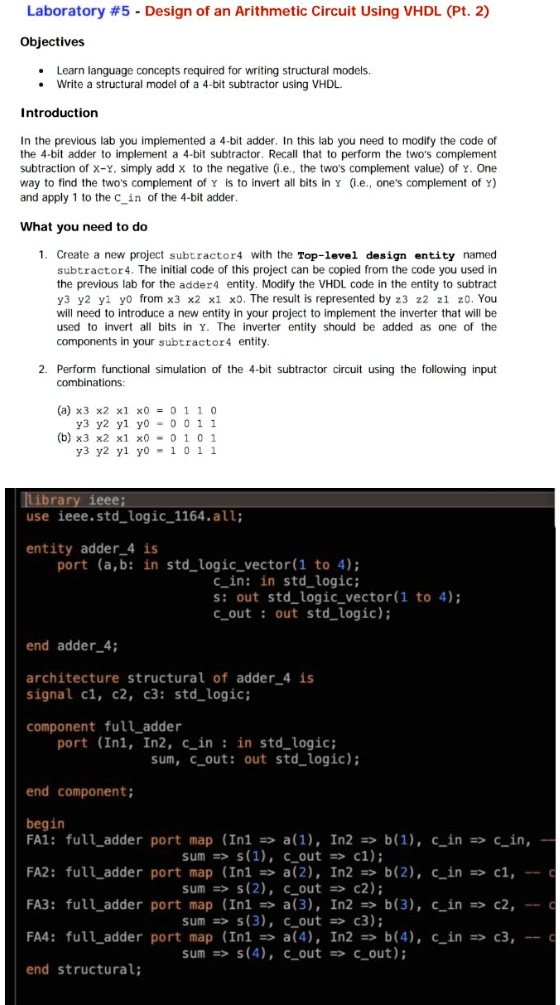

SOLVED: Please use VHDL and use the original 4-bit adder code I provided. Please add the 2's complement inverter entity and add 1 to Carry in, and make signal names according to

a. Xilinx simulated results: (i) VHDL-SVPWM generation. (ii) Inverter... | Download Scientific Diagram

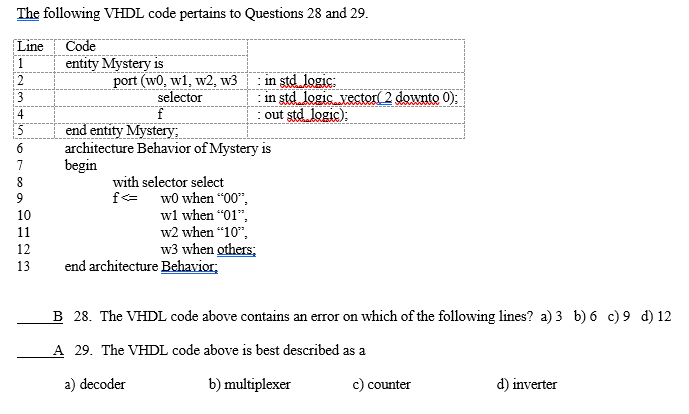

vhdl - Why use a multiplexer the select from GND and VCC instead of an Inverter? - Electrical Engineering Stack Exchange

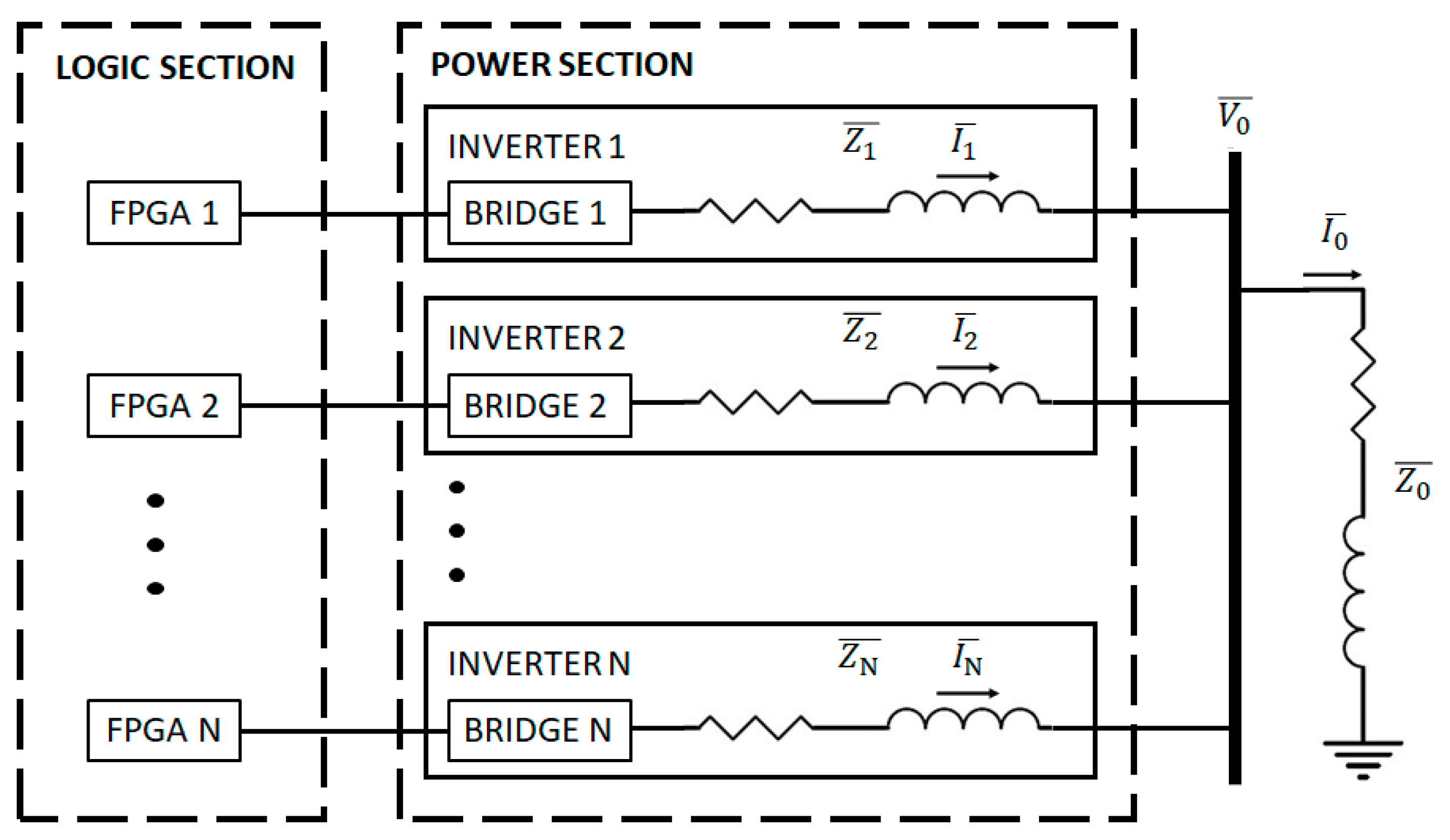

ASI | Free Full-Text | Study of a Synchronization System for Distributed Inverters Conceived for FPGA Devices

A short description of VHDL code of the framework, (a) inverter circuit... | Download Scientific Diagram

![디지털회로설계 HW4] VHDL로 inverter 구현시 transport delay와 inertial delay의 차이점 디지털회로설계 HW4] VHDL로 inverter 구현시 transport delay와 inertial delay의 차이점](https://m.reportworld.co.kr/data/preview/2013/07/data1198494_001_s.gif)